FPGA'de Statik Timing Analizi

FPGA'de Statik Timing Analizi

- 5 min read

FPGA’de Statik Timing Analizi:

Bir FPGA tasarımının güvenli ve hatasız çalışması için bazı tasarım gereksinimlerine uyulmalıdır. Bu tasarım gerekliliklerinin en önemlilerinden bir tanesi timing (zaman) analizidir.

FPGA içerisindeki register’dan register’a, FPGA içerisindeki bir register’dan harici bir donanıma giden veya harici bir donanımdan FPGA içerisindeki bir register’a gelen sinyallerin belirli zaman dilimleri içerisinde ulaşması gerekmektedir. Constraint dosyası ile tanımlanan çalışma frekansı ve üzerinde çalışılacak FPGA modelinin sabit parametrelerine göre analiz edilip tasarımın kararlı çalışıp çalışmayacağının belirlenmesine timing (zaman) analizi denir.

Timing analizi, tasarımın kararlı çalışmasını garantiye almak için önemli bir analizdir. Timing gereksinimlerini karşılamayan bir sistemde sinyaller kaynaktan hedef flip floplara doğru zamanda aktarılmayabilir ve beklenmedik davranışlar görülebilir.

Bu yazının içeriğine başlamadan önce görseller ve metinlerde kullanılan kısaltmalar ve açıklamaları aşağıda verilmiştir.

Tclk: Clock kaynağından flip flop’un clock girişine kadar olan yolda harcanan süredir. Tasarıma göre değişir.

tco (clock to output) veya tcq (clock to q): Flip flop’a gelen clock sinyalinin yükselen kenarından Q çıkışına kadar geçen süredir. Üretim teknolojisiyle alakalı, sabit bir parametredir.

Tdata: Kaynak flip flop’un Q çıkışından hedef flip flop’un D girişine kadar verinin iletilmesinde geçen süredir. Tasarıma göre değişir.

Jitter: Sinyalin özellikle değişim anlarında yaşanan dalgalanma durumudur.

Skew: İletimden kaynaklı oluşan zaman gecikmesidir.

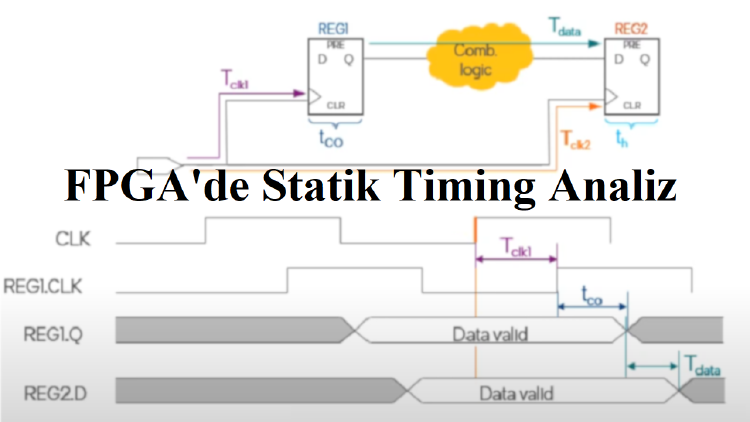

Şekil 1: Kullanılan kısaltmaların zaman çizgisi üzerinde gösterimi

Timing analizi, FPGA içerisinde bulunan flip flop’lara uygulanan sinyal girişinin (D girişi), clock girişine göre, izin verilen zaman aralığında değişip değişmediğini inceler. Setup ve hold time gereksinimleri olmak üzere iki farkı zaman dilimi için analiz uygulanır.

1. Setup time analizi:

Flip flop, kendisine uygulanan sinyal girişini örneklemek için clock sinyalinin yükselen kenarını (rising edge) kullanır. Bu yükselen kenar anındaki D girişini örnekleyerek Q çıkışına aktarır.

Gerçek hayattaki bir flip flop’ta yükselen kenar anında yapılacak örneklemenin sağlıklı bir şekilde yapılabilmesi için sinyalin değişmeden bir süre sabit kalması gerekmektedir. Bu süreye setup time süresi (tsetup) denir. Üretim teknolojisiyle alakalı, sabit bir parametredir. Clock’un yükselen kenarının hemen öncesinde yer alan bu süre içerisinde sinyal değişime uğrarsa flip flop çıkışı metastabil duruma geçerek kararsız bir hal alır. Bu kararsız durum flip flop’un çıkışının 0 veya 1 arasında değiştiği ancak belirli bir süre beklendiği taktirde çözülerek çıkışın sabit bir değer aldığı durumdur.

İzin verilen maksimum veri yolu gecikmesi (setup time için) = Trequired_setup = tco + Tdata + tsetup (flip flop’un gerektirdiği clock öncesi bekleme süresi) + diğer etmenler (jitter, skew vs.)

Trequired_setup ≤ Tclk olmalıdır.

Başka bir ifadeyle eşitsizlikteki ifadeler yer değiştirildiğinde şu şekilde de ifade edilebilir:

(tco + Tdata + tsetup) ≤ Tclk

Burada dikkat edilmesi gereken nokta, clock frekansı arttığında Trequired_setup azalmaktadır. Diğer bir ifadeyle tasarlanan veri yolu uzunluğu arttıkça clock frekansı azalmaktadır.

2. Hold time analizi:

Flip flop’un sinyal girişinin clock sinyalinin yükselen kenar anındaki örneklemeden sonra bir süre sabit kalması gerekmektedir. Bu süreye hold time süresi (thold) denir. Üretim teknolojisiyle alakalı, sabit bir parametredir. Flip flop’un D girişindeki sinyalin clock’un yükselen kenarının hemen öncesinde yer alan bu süre içerisinde değişime uğraması durumunda flip flop çıkışı metastabil duruma geçerek kararsız bir hal alır.

İzin verilen minimum veri yolu gecikmesi (hold time için) = Trequired_hold = thold (flip flopun gerektirdiği clock sonrası bekleme süresi) + diğer etmenler (jitter, skew vs.)

Diğer bir ifadeyle, verinin kaynak flip-flop’tan oluşturulup hedef flip-flop’a iletilmesinde geçen süre, minimum hold time süresinden (ve sistem belirsizliklerinden) daha uzun veya eşit olmalıdır:

(tco + Tdata) ≥ Trequired_hold

Burada dikkat edilmesi gereken nokta, clock frekansının Trequired_hold‘a herhangi bir etkisinin olmadığıdır çünkü aynı clock kenarında yapılan örnekleme ile ilgili bir parametredir.

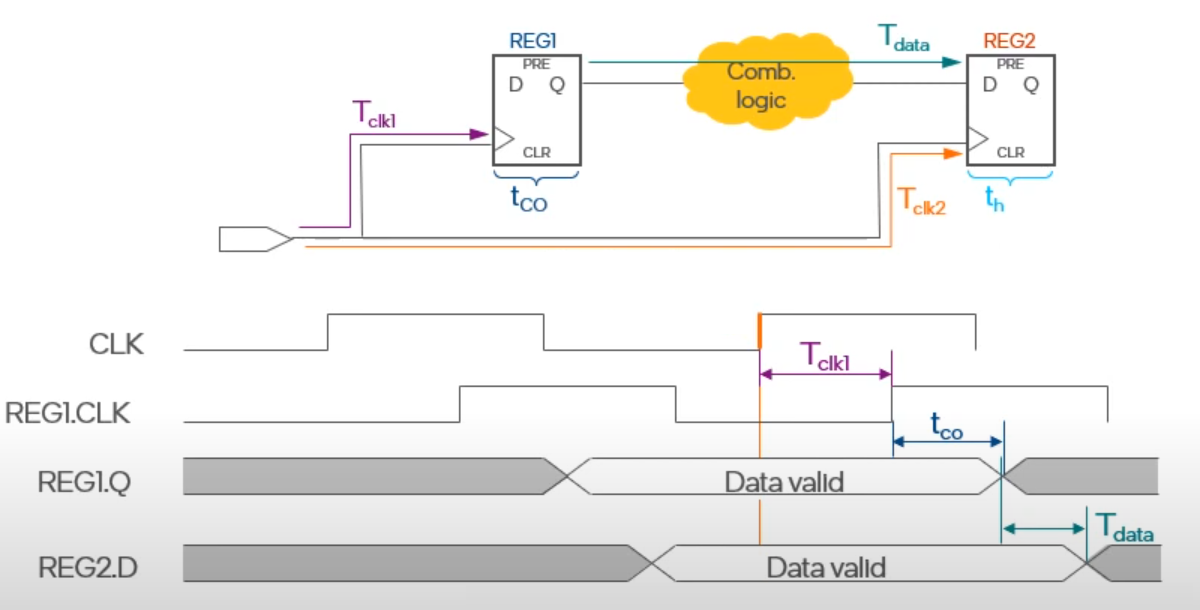

Yani setup ve hold time clock örneklemesi esnasında stabil kalınması gereken zaman kurallarının kontrolüdür. Aşağıda flip flop’un sinyal girişinin stabil kalması ve değişmesine izin verilen zaman aralığı gösterilmiştir.

Şekil 2: Flip flop'un sinyal girişinin stabil kalması ve değişmesine izin verilen zaman aralığı(1)

Setup ve hold time analizi hesaplamasının nasıl yapıldığı konusundan önce setup ve hold time gereksinimlerini karşılayıp karşılamadığı bakımından çeşitli örnekler aşağıda incelenmiştir.

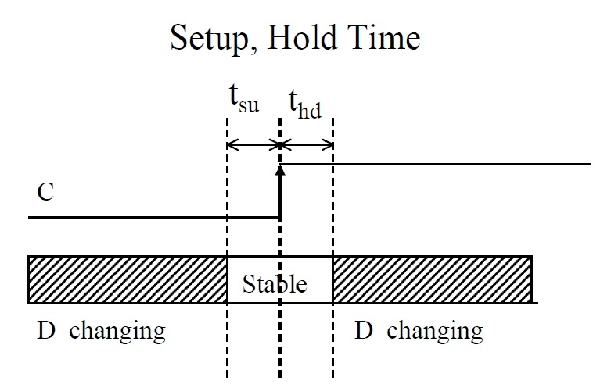

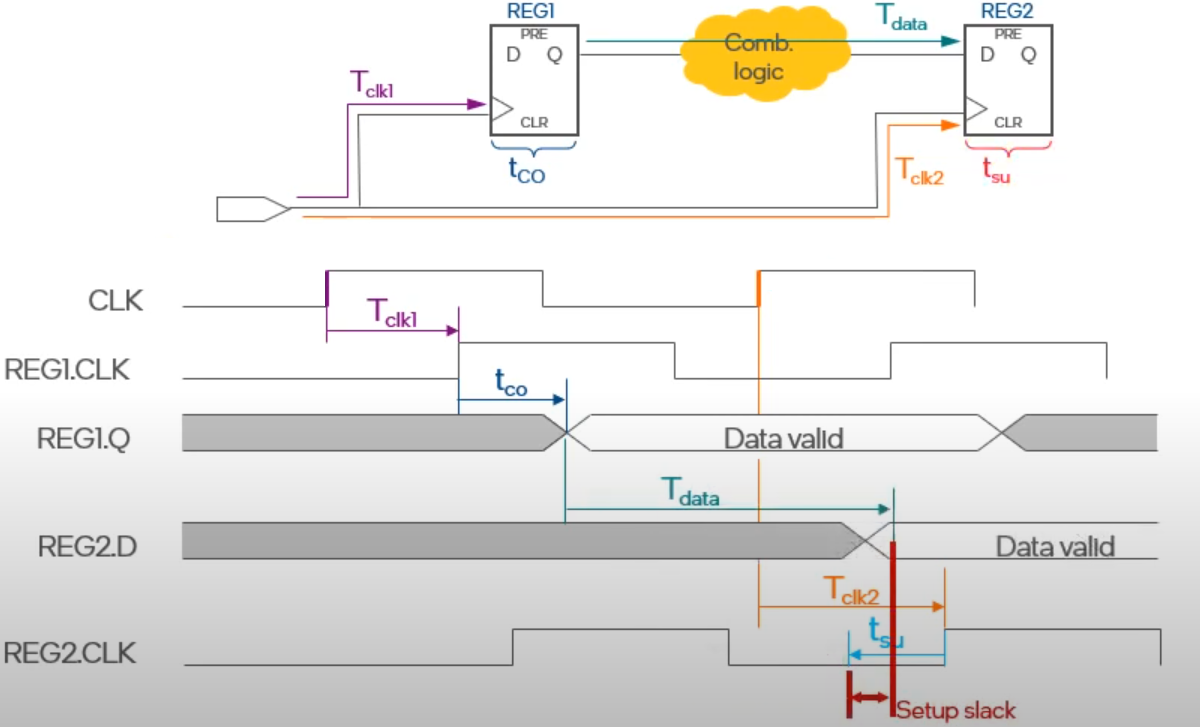

Setup time bakımından incelenen ve hatasız çalışan bir örnek aşağıda verilen Şekil 3 üzerinde gösterilmiştir.

Şekil 3: Setup time bakımından hatasız çalışan bir örnek

Görseldeki zaman çizelgesindeki sinyaller incelendiğinde Register 1’den çıkan REG1.Q sinyali REG2.D girişine geldiğinde bir sonraki örneklemeye Tsetup’tan daha uzun zaman kalmaktadır. Dolayısıyla setup time bakımından herhangi bir ihlal bulunmamaktadır.

Setup time bakımından incelenen ve setup time ihlalı olan bir örnek aşağıda verilen Şekil 4 üzerinde gösterilmiştir.

Şekil 4: Setup time ihlali olan bir örnek

Görseldeki zaman çizelgesindeki sinyaller incelendiğinde Register 1’den çıkan REG1.Q sinyali REG2.D girişine geldiğinde bir sonraki örneklemeye Tsetup’tan daha kısa zaman kalmaktadır. Dolayısıyla örnekleme öncesinde gereken sinyal stabilliği sağlanamamış, setup time bakımından ihlal gerçekleşmiştir.

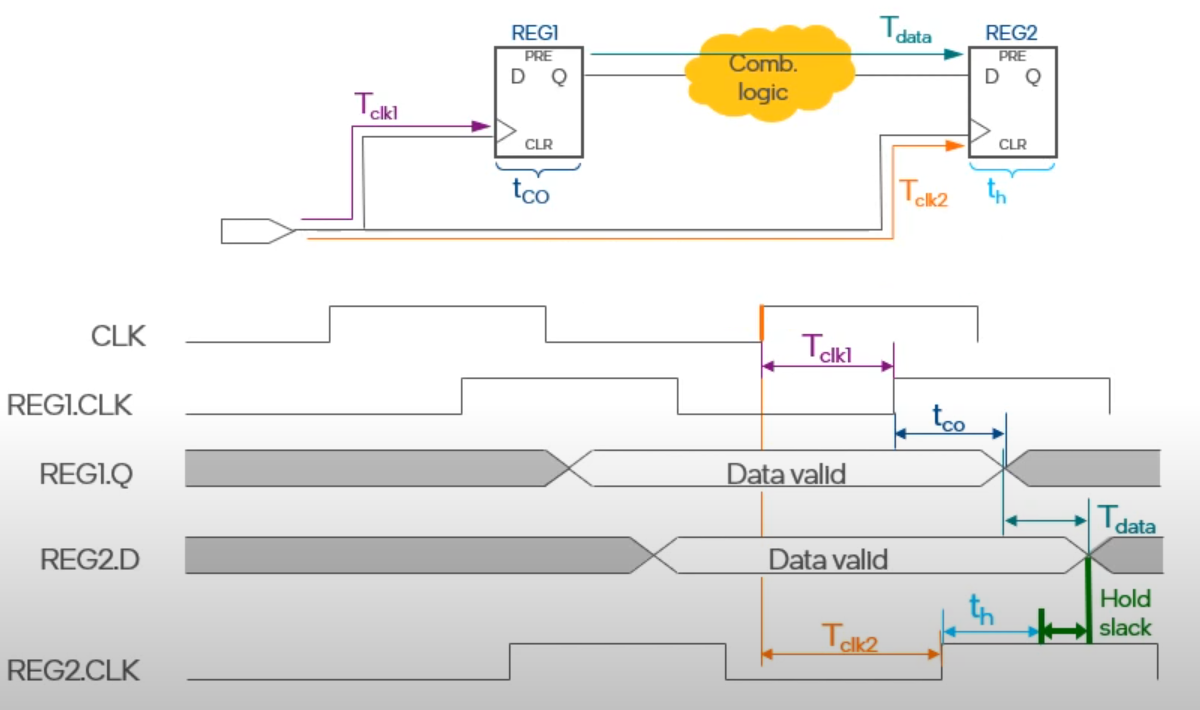

Hold time bakımından incelenen ve hatasız çalışan bir örnek aşağıda verilen Şekil 5 üzerinde gösterilmiştir.

Şekil 5: Hold time bakımından hatasız çalışan bir örnek

Görseldeki zaman çizelgesindeki sinyaller incelendiğinde Register 1’den çıkan REG1.Q sinyali REG2.D girişine gelip bir sonraki clock yükselen kenarıyla birlikte örneklendiğinde, thold’tan daha uzun bir süre boyunca sabit kalmaktadır. Dolayısıyla hold time bakımından herhangi bir ihlal bulunmamaktadır.

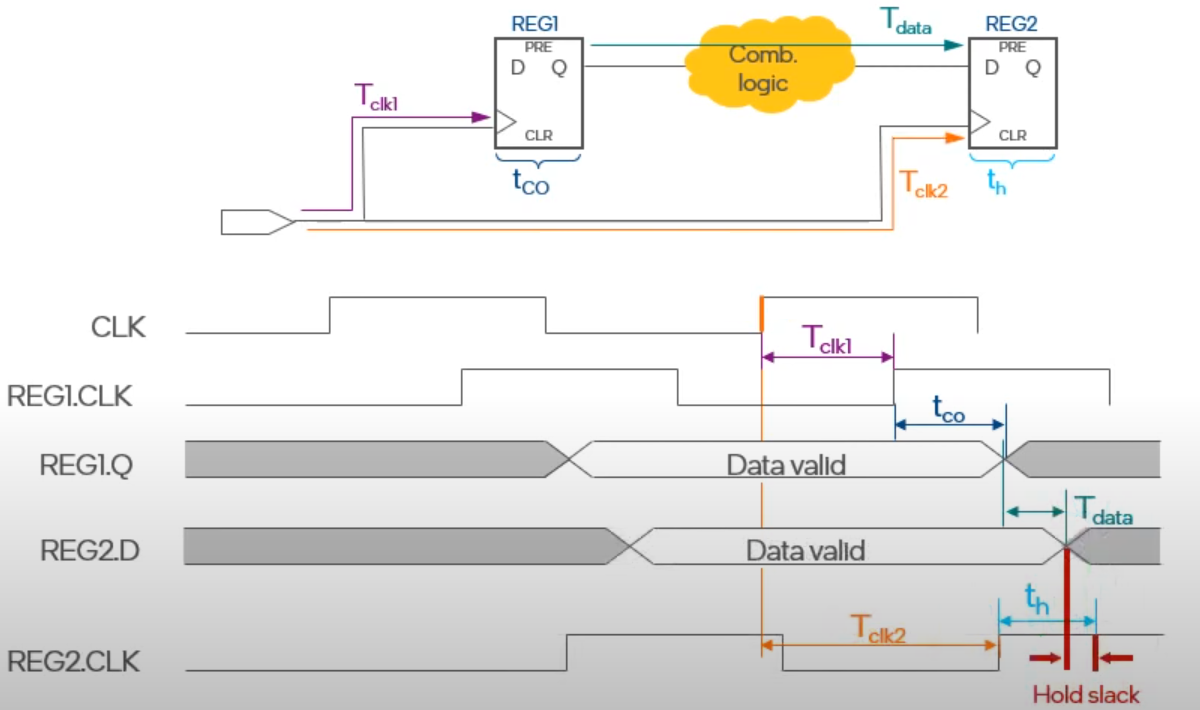

Hold time bakımından incelenen ve hold time ihlali olan bir örnek aşağıda verilen Şekil 6 üzerinde gösterilmiştir.

Şekil 6: Hold time ihlali olan bir örnek

Görseldeki zaman çizelgesindeki sinyaller incelendiğinde Register 1’den çıkan REG1.Q sinyali REG2.D girişine gelip bir sonraki clock yükselen kenarıyla birlikte örneklendiğinde, thold’tan daha kısa bir süre boyunca sabit kalmaktadır. Dolayısıyla örnekleme sonrasında gereken sinyal stabilliği sağlanamamış, hold time bakımından ihlal gerçekleşmiştir.

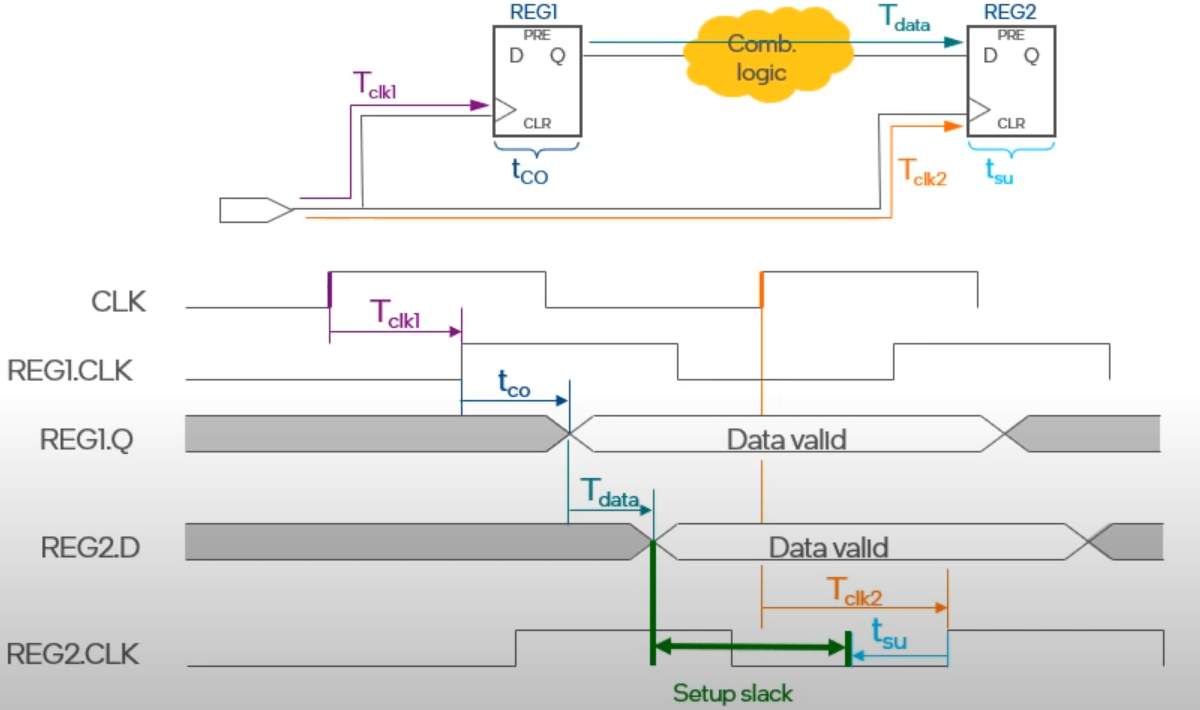

Setup ve Hold time analizi yapılırken analiz araçları her bir veri yolu için slack(boşluk miktarı) hesabı yapar. Bu slack hesaplarında kullanılan parametreler ve hesaplanışları aşağıda verilmiştir.

Setup Slack: Gereken veri aktarım süresi (setup time için) - Verinin varış süresi ===> Verinin varış süresi ≤ Trequired_setup olmalıdır.

Hold Slack: Verinin varış süresi - Gereken veri aktarım süresi (hold time için) ===> Verinin varış süresi ≥ Trequired_hold olmalıdır.

Setup ve hold slack değerleri pozitif olduğunda tasarım timing gereksinimlerini karşılamakta, aksi halde tasarımda timing ihlali bulunmaktadır.

Pozitif setup ve hold slack değerlerinde tasarımın kararlı çalışması garanti altına alınırken negatif slack değerlerinde sistemde metastability ve kararsız durumlar gözlenebilir. Bu durum flip flop’ların çıktılarının kararsız olmasına, kararsız flip flop’lardan örnekleme yapan başka flip flop’ların yanlış değerleri örneklemesine ve sistemin çökmesine kadar ilerleyen bir hataya yol açabilir. İyi bir tasarımda bu hatalara karşı analizleri dikkate almak önem arz eder.

Bu yazıdaki içerik ve görseller için YouTube’da paylaşım yapan Altera kanalının Understanding Timing Analysis in FPGAs videosundan faydalanılmıştır. (1): Görsel vlsi-expert adresinden alınmıştır.